XVF3500硬件设计

阅读前确认

用户需要确认一下内容,以方便阅读下文

- 已拥有了pxvf3500-KIT,且查阅pxvf3500-KIT_硬件使用

- 已详细了解XVF3500 内置的前端算法AEC , BF , NS, AGC,,且已查阅pxvf3500-KITdsp描述

- 已查阅本站XVF3500项目实施落地

- 已查阅了XVF3500的datasheet和参考设计

- 已确认XMOS XVF3500 4路麦克风阵列方案性能可满足导入项目产品中

XVF3500 datasheet 导读

查看XVF3500-FB167-Datasheet_1.2.pdf,其描述的为XVF3500裸片(不含固件)的硬件特性。了解基本的硬件数据,电气特性。

基本特性

- 商用温度等级(0 °C to 70 °C)

- FBGA 167 封装

- 685mA典型工作电流,1W左右(固件运行)

- I/O 驱动能力为4mA

- 订购型号:XVF3500-FB167-C; 丝印:VSM05C

电源

根据datasheet的最小系统框图,XVF3500的需要两路电压供应,3V3和1V0, 其中3V3提供给I/O, USB , Flash等外设使用,1V0提供给XVF3500逻辑核心使用。

其两路电压时序要求为3V3先上电,稳定后,1V0后上电。

复位检测

XVF3500需要外部有复位检测芯片,可以选择单独侦测 3V3或者1V0,以避免在电压不正常时,芯片无法复位来运行固件。

QSPI Flash

XVF3500需要外置QSPI Flash(类似GD25Q16或者IS25LP016D),其主要是存储XVF3500固件,所以XVF3500项目得预先烧录固件才能启动运行4路麦克风阵列算法。

使用QSPI Flash烧录器烧录XVF3500需要配置QE=1的烧录方式。

BOOT MODE

XVF3500的需要读取QSPI Flash芯片程序来启动,根据框图连接XVF3500和Flash时,需要确保QSPI_CS引脚上拉1K电阻,以实现boot mode是由XVF3500芯片读取加载内部的QSPI Flash固件。

I/O 映射

XVF3500的逻辑I/O接口的功能使用由固件定义,datasheet 无描述I/O 功能使用,需参考木瓜电子或者XMOS官方提供的的原理来选择使用特定的I/O map。

时钟信号

XVF3500外部需要24MHz有源晶振接入作为启动晶振,接入到CLK 引脚,而音频时钟16KHz 和48KHz采样率仍需要一个外部的12.2888MHz音频时钟或者晶体接入作为I2S或者PDM麦克风的MCLK时钟使用。

原理图和PCB

根据我司或者XMOS官方的提供的参考原理,结合XVF3500的datasheet最小系统。用户可以比较轻易完成XVF3500的最小系统设计,包含了电源,时钟,启动上拉等。

原理图设计

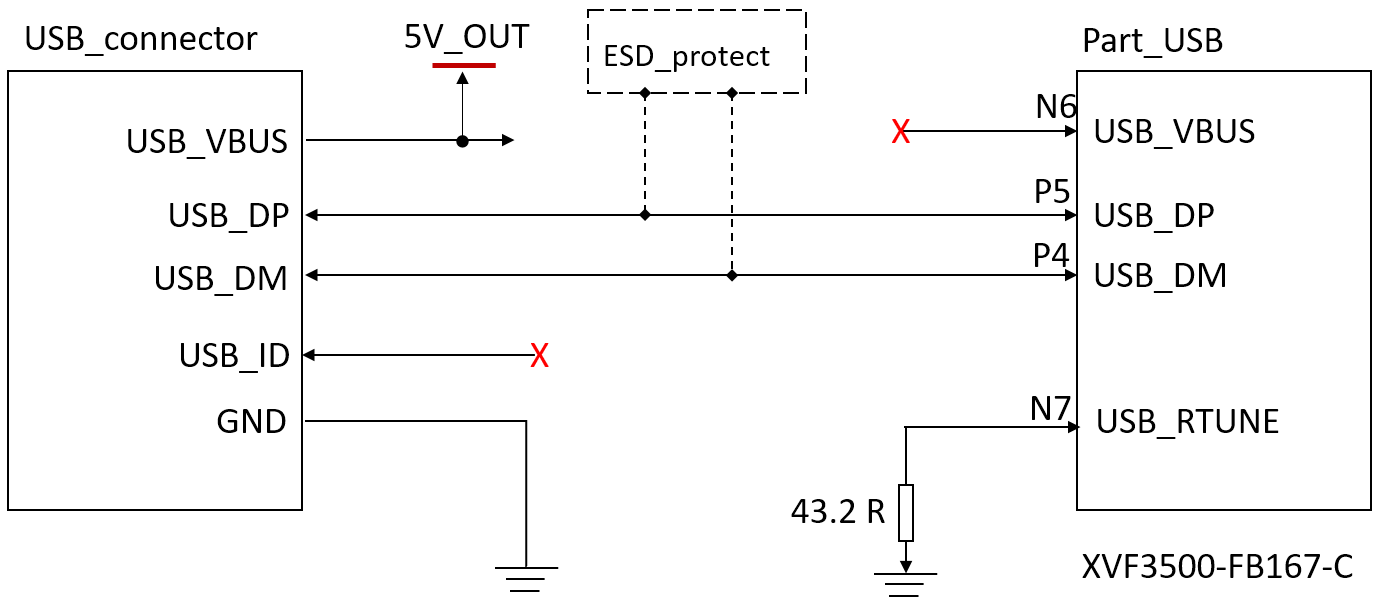

USB 接口设计

在XVF3500 条形4路麦克风阵列方案中,USB接口除了提供5V电源供应,USB接口仍需要用来作为音频传输,DFU固件,vfctrl调试参数。 XVF3500 芯片内部集成了USB PHY收发器,可以直接使用芯片引脚USB_DM,USB_DP,USB_VBUS,USB_RTUNE连接外部USB端子。

遵循XVF3500 datasheet说明,USB的设计分为USB供电或者外部电源作为XVF3500芯片供电两种情况,如图为USB作为整个XVF3500系统供电原理设计

根据XVF3500 datasheet的描述

- USB_RTUNE 需要下拉43.2 R电阻

- USB_VBUS 不能连接,需悬空

- USB_VBUS提供5V给DC-DC 转换3V3和1V0电源提供给XVF3500和外围芯片

- 因为XVF3500 的ESD压力为2KV,建议用户在USB端子设计加入ESD保护电路芯片

如内部有电池或者外部供应5V给整个电源系统,则USB_VBUS的设计需要参考XVF3500 datasheet(page 19)的USB_VBUS设计。

The 10k series resistor and 0.1uF capacitor ensure than any input transient is filtered and does not reach the device. The 47k resistor to ground is a bleeder resistor to discharge the input capacitor when VBus is not present. The 1-10uF input capacitor is required as part of the USB specification. A typical value would be 2.2uF to ensure the 1uF minimum requirement is met even under voltage bias conditions

如用户决定使用XVF3500使用I2S输入输出来连接host主控(ARM,BT,WiFi等芯片)代替USB作为音频传输,同时强烈建议前期保留USB端子以便进行dfu_usb和vfctrl_usb使用。后期确定量产时再去掉USB部分。

电源设计

XVF3500 内部无DC-DC和LDO集成,需要外部提供3V3和1V0的供电。其中3V3提供给XVF3500及其集成的部分的 I/O供电,1V0供应XVF3500核心及其集成组件的核心使用。查看datasheet的5 Example Application Diagram的框图,得到XVF3500电源的需求情况。

3V3 供应部分 3V3电压范围(3.135 ~ 3.465 V)

- VDDIO (3V3) : Digital I/O power

- OTP_VCC (3V3) :pins for OTP

- USB_VDD33 (3V3) : USB Analog power,analog supply to the USB-PHY

1V0 供应部分 1V0电压范围(0.95 ~ 1.05 V)

- VDD pins (1V0):Digital tile power ,for the core logic

- PLL_AVDD (1V0) : Analog power for PLL, pins for the PLL

- USB_VDD (1V0) : USB Digital tile power , supply to the USB-CORE

查看datasheet的Power Consumption 部分得到XVF3500的核心供电需求电流为600 mA左右(700mA MAX), 确保DC-DC电源芯片1V0输出需要大于700mA,建议值1A的输出能力,且不能使用LDO电源芯片输出1v0,导致损耗过大。 根据datasheet所述的3V3和1V0的上电时序要求,我们建议整体电源设计的时序为3V3先上电,然后使能(enable)1v0后上电

其电源设计如下图,其中

- 3V3由5V DC-DC转换得到,3V3先稳定后,使能另一个DC-DC转换得到1V0 ; 形成 3V3先上电,1V0后上电的时序

- 3V3和1V0分别供应相应的电源输入引脚,尽量保证每个电源输入引脚有个104的滤波电容,且这些电容在layout的时候,尽量靠近相应的电源引脚。

- pin 50 和 pin 65 必须悬空,不能接任何电气

- PLL_AVDD 需要一个高品质的电源,在PLL_AVDD引脚加入RC 低通滤波器,且在layout的时候,4R7电阻和104电容需要尽可能靠近PLL_AVDD引脚

系统设置

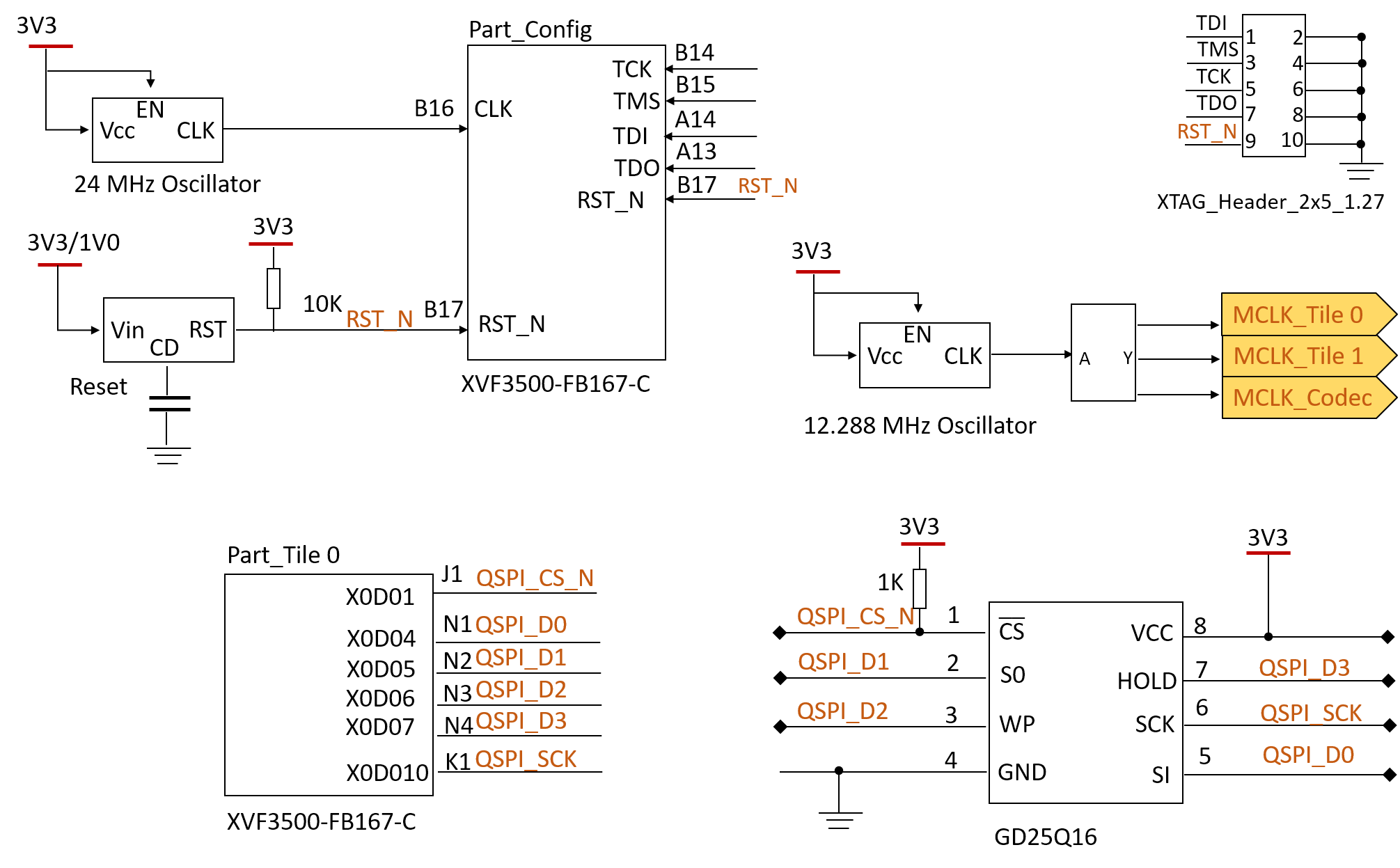

XVF3500外围需要两个有源晶振,24 MHz 和 12.288 MHz:

- 24 MHz时钟为XVF3500起振时钟,提供给内部PLL产生芯片主频,24 MHz有源晶振输出接入XVF3500的CLK 引脚。

- 12.288 MHz时钟为XVF3500核心(Tile 1 和Tile 2)处理音频传输协议需要的音频时钟,XVF3500核心将12.288 MHz进行分频,分别生成I2S 的 LRCLK , BCLK 和 PDM 协议的CLK。 所以12.288 MHz需要分出多路时钟出来,作为MCLK分别输入到XVF3500 Tile 1 ,Tile 2 和ADC/DAC使用。

XTAG接口为XMOS专用的调试和烧录工具,XVF3500需要下使用XTAG烧录factoy固件到外置的QSPI Flash芯片了后,XVF3500才能正常运行麦克风阵列算法,在原理设计时,需要引出XTAG接口,以便样机时调试和烧录XVF3500固件。

XVF3500外部需要有个复位检测芯片,避免供电电压不正常时导致固件运行紊乱,根据datasheet的描述,其复位时间必须为1ms~10ms之间的拉低时间

If your design is powered by VBUS,then RST_N should go high within 10 ms of attaching to VBUS in order to ensure that USB timings are met. RST_N should be at least 1 ms after VDDIO good to enable the built-in flash to settle.

由于XVF3500的级联特殊要求(XMOS的芯片的Tile2与Til1 级联,共同访问外部QSPI Flash芯片),XVF3500的X2D06必须上拉电阻,

其整体设计为, 其中:

- XTAG 建议接一个2x5 1.27mm的母座端子引出,方便烧录和调试,且脚位排序不变

- QSPI_CS_N需要上拉1K电阻, 确保XVF3500上电时能够访问外部的QSPI Flash

- 12.288 MHz有源晶振时钟分出3路时钟,分别提供Tile 0,Tile 1和Codec作为MCLK使用,如果PCBA板子布线较长,建议加个buffer logic器件加以增大驱动能力

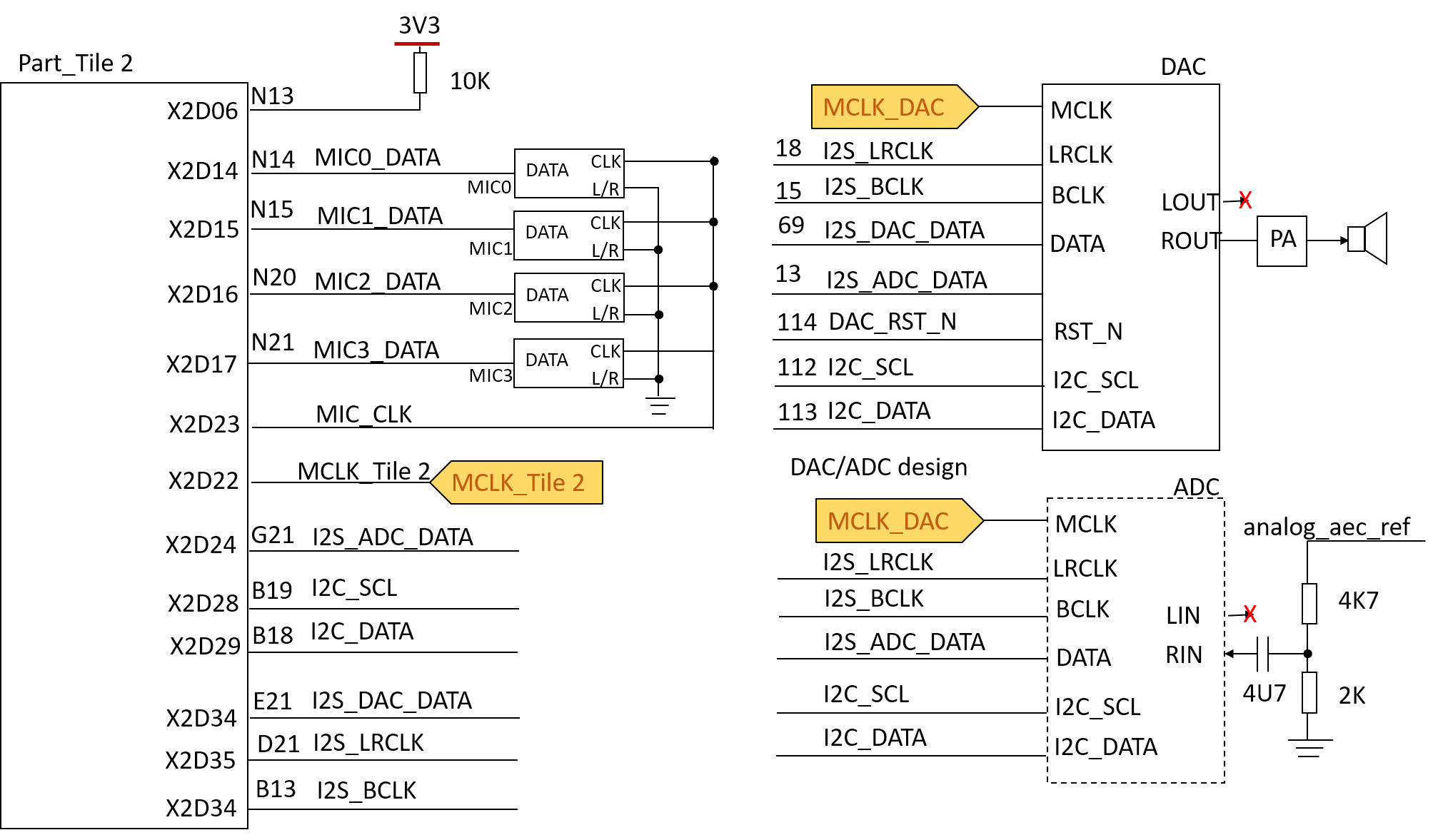

音频I/O

XVF3500 支持多路PDM麦克风,但是XMOS官方vocal Fusion算法仅支持4路麦克风阵列算法。多路PDM麦克风接口复用1个clk 时钟信号线,以确保多路麦克风信号高一致性。多路麦克风data信号线各自独立,不分L/R时序。

XVF3500 支持2路I2S 接口,其I2S协议为标准I2S, 64fs, 有效位可以实现16bit/24bit。 如果I2S连接ADC或者DAC, 则XVF3500 的I2S为master模式 ; 如果XVF3500 连接蓝牙/wifi/CPU, 则XVF3500都可以选择master/slave模式。两路I2S都复用MCLK , LRCLK , BCLK。

其中XVF3500的音频接口PDM和I2S的时钟频率为: PDM_CLK: 3.072 MHz I2S_MCLK: 12.288 MHz I2S_BCLK: 1.024 MHz(@16KHz sample rate) I2s_LRCLK: 16 KHz(@16KHz sample rate)

XVF3500的DAC和ADC选型设计,根据用户项目框架的需要,参考本站XVF3500项目实施落地的应用框架而确定是否都需要ADC和DAC的设计。可以简单理解为:

- 需要XVF3500作为UAC设备播放声音,则需要加上DAC

- 需要接模拟信号作为XVF3500作为AEC参考信号,则需要加上ADC

选择相应的DAC和ADC需要吻合XVF3500的I2S时序,且尽量免I2C配置,为I2S自适应的Codec,避免XVF3500固件有过多的I2C配置造成软件工程师过多投入。

其整体设计如下图,其中:

X2D06(pin N13)为上章提到的XVF3500所需的上拉,在下图体现出来。

每个所用到的I/O都是XVF3500软件定义,由于需要配合现成的固件,所以I/O不建议更换

4个PDM 麦克风的LR 引脚都需要统一拉低接地。如成本允许,单独生成3V3A干净电源提供给麦克风供电。

pxvf3500-KIT评估板麦克风布局为33.3mm的条线均匀分布,如需其他条形尺寸,麦克风的间距不小于30 mm,其最大间距由TTL受干扰限制,不建议太大,XVF3500 I/O驱动能力仅为4mA。如更改了麦克风的间距尺寸,需要通知固件方修改软件以匹配阵型

用户根据项目框架需要是否DAC

用户根据项目框架需要是否ADC,并且建议模拟参考信号(analog AEC ref)在播放的运放前端接入,同时建议设计分压电路,查看ADC的满框输入水平(Full Scale Input Level ),以确定模拟信号进行分压时,匹配相应的电阻值

用户尽量选择免I2C配置的ADC和DAC,选择I2S自适应的Codec,则不需要通知固件方进行I2C配置来吻合XVF3500的I2S协议和驱动Codec

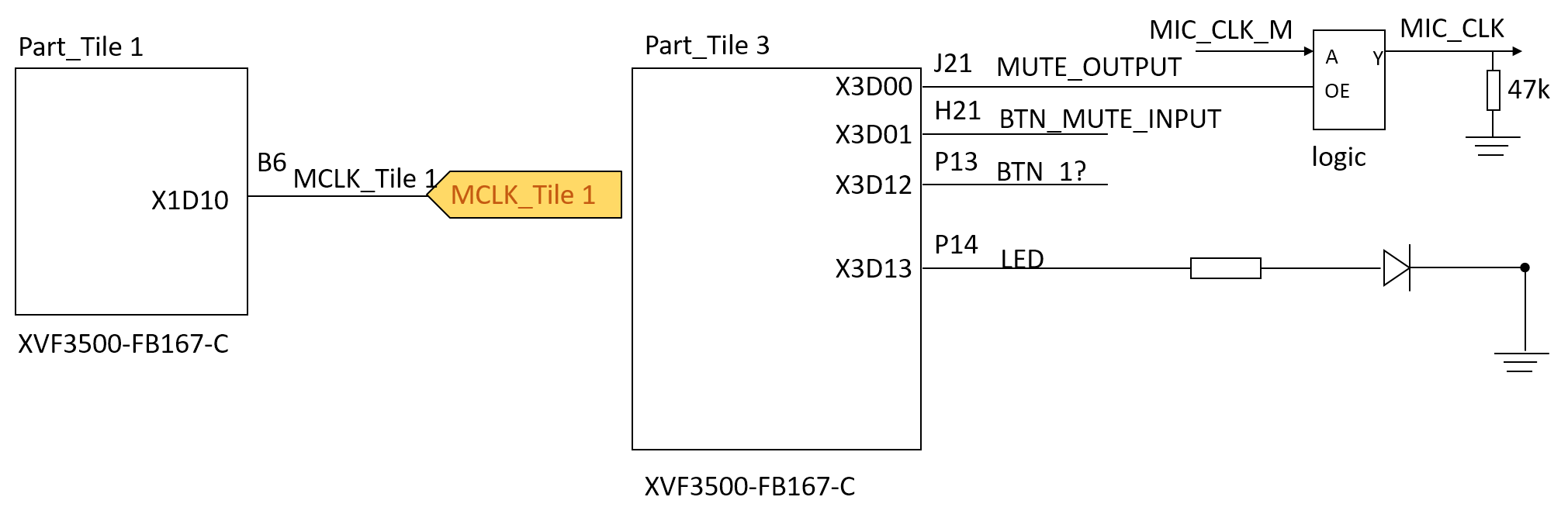

控制I/O

XVF3500固件内部仍有小些逻辑控制资源,可以实现控制LED,按键等功能。LED的控制主要VAD(人声检测)指示使用。

按键控制建议仅用在麦克风的静音(MUTE信号)。如功能上需要用到麦克风静音功能,建议在4路PDM复用的CLK引脚加上逻辑器件,实现电气上的静音。

其整体设计如下图,其中:

补充MCLK_Tile 1 接入到X1D10, XVF3500 Til0 运行16 KHz的麦克风阵列算法,需要外部提供音频时钟信号。

LED为VAD(人声检测)指示使用,如不需要LED指示,可全部去掉

MIC_CLK拉高拉低都可以实现麦克风信号静音(MUTE),这里建议用户增加逻辑logic器件来实现物理上MUTE。不建议在XVF3500固件来时间音量+,音量—,会涉及投入比较大的固件开发。如需要,建议直接控制运放。

检查表 Check List

框架检查

- USB 需要做保留设计,无论是是否有使用I2S作为音频传输,USB的dfu_usb和vfctrl_usb仍需要使用

- XVF3500的XTAG设计建议使用2x5母座端子,间距1.27mm;或者2x10的2.54mm的母端子,避免留出测试点接线麻烦的方式。木瓜电子可提供转接板,同时用户需要购买XTAG烧录器

- XVF3500需要置了QSPI Flash,样机或者量产前,需提前烧录XVF3500的固件到QSPI Flash芯片上,同时确保使用QSPI flash烧录方式QE=1的配置烧录。要求用户需要拥有flash烧录器,类似硕飞的SP8-B等设备。

- 确认好AEC ref的提供给XVF3500的方式,以便确认是否ADC和DAC

原理图和PCB检查

- 查阅XVF35000的datasheet的Check list(page 74)

- 查阅XVF35000的VocalFusion Speaker Hardware Manual.pdf

- 复位芯片是必须要的,可以选择侦测3V3和1V0

- 麦克风layout布局,建议每个麦克风间距不小于30mm

- Layout时,USB型号尽量并行走线且不靠近I2S/PDM的时钟线

- Layout时,需要考虑量产时,麦克风需要加上密封胶套来配合结构外壳,达到声学要求

PCBA问题排查

USB不能正常枚举出声卡设备

- 确认硬件的电源3V3和1V0是否正常; 确认24 MHz时钟正常进入XVF3500; 确认复位检查芯片是否拉住了XVF3500的复位

- 确认XVF3500是否已有固件;确认使用QSPI Flash烧录器烧录固件时,配置QE=1,并且烧录时已把配置烧录进去。XVF3500已烧录固件时,板载5V电源会在大于150mA

判断麦克风是否良好

- 烧录或者dfu_usb一个8通道固件,把4个麦克风原始信号在audactiy录制查看,或者使用AP分析

AEC 性能不好

- 如是模拟参考信号到ADC提供给XVF3500的方式,确认ADC接收到的模拟参考信号是否正常,是否有作为分压输入水平不超过ADC的满框输入水平

- 如是USB提供参考信号给XVF3500的方式,确保DAC或者功放不能有EQ处理再喇叭播放。

- 确认整个过程中喇叭和麦克风的相对位置没有任何变动

- 确认喇叭到麦克风声压不大于100dB

- 确认麦克风有足够好的密封性

服务

XVF3500的硬件设计用户需要自行完成,结合木瓜电子提供的参考原理图设计(pxvf3500-KIT 评估板),XVF3500 datasheet和VocalFusion Speaker Hardware Manual文档完成设计。

木瓜电子可以为用户提供XVF3500 固件,整体设计如有技术问题,可以发邮件发mic@pawpaw.cn咨询。

木瓜电子可以提供XMOS XVF3500 , 麦克风和Code芯片供应服务。